# FAIRCHILD

# MACROLOGIC BIPOLAR MICROPROCESSOR DATABOOK

# **TABLE OF CONTENTS**

|                                                                                                                                                                                                                           | Page                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SECTION 1                                                                                                                                                                                                                 |                                      |

| Introduction                                                                                                                                                                                                              | 1-3                                  |

| SECTION 2 – DEVICE INDEX AND SELECTOR INFORMATION                                                                                                                                                                         |                                      |

| Numerical Index of Devices Device Selector Guide by Function Functional Building Blocks by Technology Memory Products Selector Guide                                                                                      | 2-4<br>2-4                           |

| SECTION 3 – BIPOLAR MACROLOGIC                                                                                                                                                                                            |                                      |

| General Description and Features  I³L Technology  Design Considerations  Definition of Symbols and Terms  Device Data Sheets                                                                                              | 3-3<br>3-4<br>3-8                    |

| SECTION 4 – CMOS MACROLOGIC                                                                                                                                                                                               |                                      |

| General Description and Features Isoplanar C Technology Design Considerations JEDEC Industry Standard "B" Series CMOS Definition of Symbols and Terms 4700 Series CMOS Family Characteristics Device Data Sheets          | 4-3<br>4-3<br>4-8<br>4-11<br>4-13    |

| SECTION 5 – MACROLOGIC APPLICATIONS                                                                                                                                                                                       |                                      |

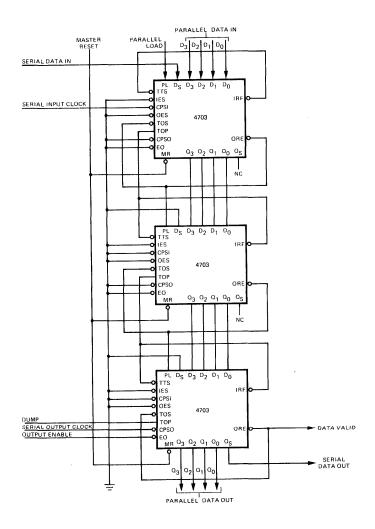

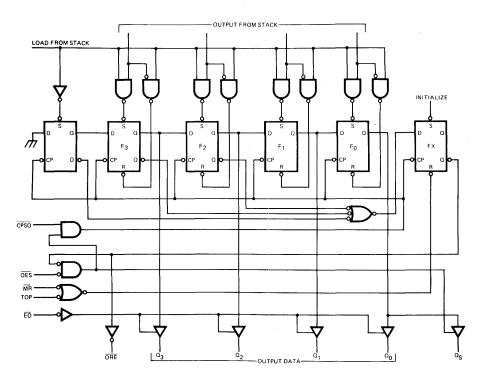

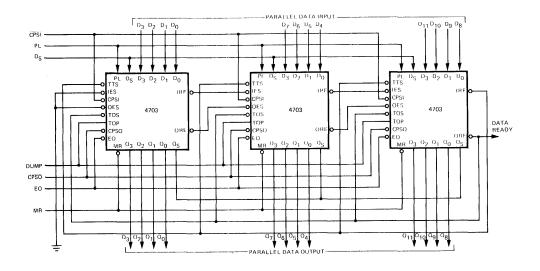

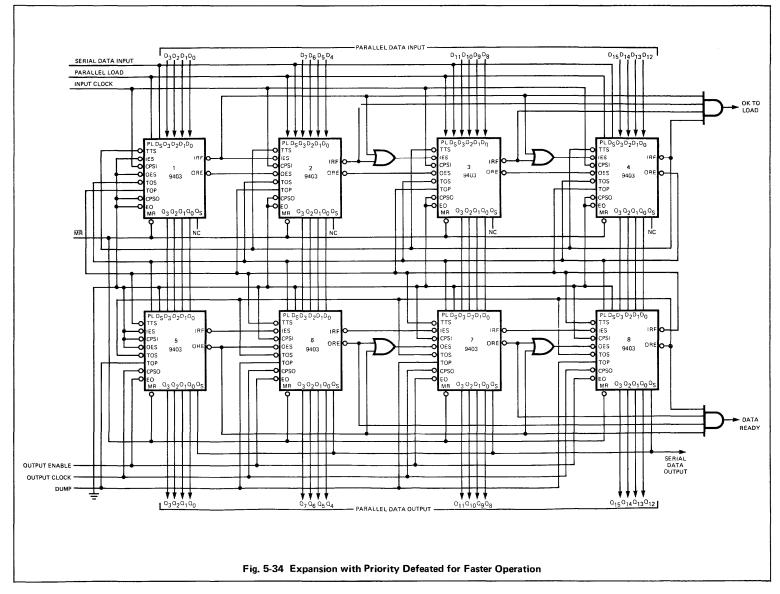

| Microprogramming with Macrologic Implementing Data Paths with Macrologic A Simple Processor Example Macrologic Assemblers Cyclic Checks for Error Detection Programmable Bit-Rate Generator Using the 9403 and 4703 FIFOs | 5-14<br>5-16<br>5-20<br>5-21<br>5-29 |

| SECTION 6                                                                                                                                                                                                                 |                                      |

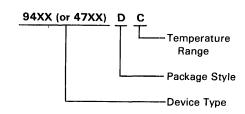

| Order and Package Information                                                                                                                                                                                             | 6-3                                  |

| SECTION 7                                                                                                                                                                                                                 |                                      |

| Fairchild Field Sales Offices Perrosentatives and Distributors                                                                                                                                                            | 7 0                                  |

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| DEVICE INDEX AND<br>SELECTOR INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| BIPÖLAR MACROLOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| CMOS MACROLOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |

| APPLICATIONS: 1997 Property of the second se | 5 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

| ORDER AND PACKAGE INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 6 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |

FAIRCHILD FIELD SALES OFFICES, REPRESENTATIVES AND DISTRIBUTORS

# INTRODUCTION

Microprogramming is a practical method for implementing as many system functions as possible in one "centralized" logic block that is controlled by "instructions" stored in a memory. This is accomplished using a mixture of hardware and software techniques. Since designing microprogrammed systems with SSI/MSI is rather difficult and tedious, in the past there has been only limited use of microprogramming except by sophisticated users. Recently, however, the dramatic increase in digital-system complexity has opened up the field of microprogramming and the proliferation of available microprocessors has greatly simplified the designer's task. While focus has been on the MOS microprocessor families, interest is now moving toward the higher speed bipolar bit-slice microprocessors for microprogrammed system design. Where ultra-low power consumption and high noise margin are crucial factors, CMOS bit-slice microprocessors are gaining popularity.

Fairchild Macrologic is an LSI bit-slice family designed for optimum performance, versatility and system-cost effectiveness. The main goal in its development was to provide a set of functional building blocks that the typical design engineer frequently required but formerly had to implement with SSI and MSI. In some cases, this amounted to a straightforward combination of a number of existing MSI onto a single chip; for example, the ALRS — the foundation of the bipolar microprocessor chip set. The ALRS combines ALU, RAM, 3-state registers, and decode logic to form a fast 4-bit CPU. Other functions, however, differed considerably from existing SSI and MSI devices and consequently were difficult and expensive to implement. An example of this is the cyclic redundancy checker—a combination of shift register, ROM and exclusive-OR logic that provides the error-detecting function on one chip.

Once the functions were determined, the most appropriate technology for a particular function was selected. In some cases, low power Schottky was chosen; in some, Isoplanar Integrated Injection Logic (I³L™); in others, CMOS or Isoplanar Schottky. Certain functions turned out to be feasible in two or more of these advanced technologies.

This databook is divided into four major sections. The first (Section 2) includes selector information for locating functions and available technologies for a given function. Also, since all Macrologic applications require memory circuits, a list of Fairchild memories is included. Section 3 contains bipolar Macrologic (advanced Schottky TTL and I³L) data sheets. Section 4 includes the CMOS Macrologic data sheets. To illustrate the versatility of this bit-slice family, the final technical section (Section 5) introduces the reader to a few of the many Macrologic applications. It is important to realize that Macrologic can be used to implement highly sophisitcated microprogrammed digital systems, and the list of applications is virtually endless.

| INTRODUCTION                                                    |   |

|-----------------------------------------------------------------|---|

|                                                                 |   |

| DEVICE INDEX AND SELECTOR INFORMATION                           | 2 |

| GEESTON IN ORMATION                                             |   |

| BIPOLAR MACROLOGIC                                              | 3 |

|                                                                 |   |

| CMOS MACROLOGIC                                                 | 4 |

|                                                                 |   |

| APPLICATIONS                                                    | 5 |

|                                                                 |   |

| ORDER AND PACKAGE INFORMATION                                   | 6 |

|                                                                 |   |

| FAIRCHILD FIELD SALES OFFICES, REPRESENTATIVES AND DISTRIBUTORS | 7 |

# 2

# **NUMERICAL INDEX OF DEVICES**

| DEVICE NO. | DESCRIPTION                                     | PAGE |

|------------|-------------------------------------------------|------|

| 4702       | Programmable Bit-Rate Generator                 | 4-17 |

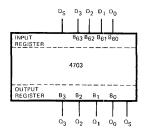

| 4703       | 16 x 4 Parallel/Serial FIFO                     | 4-25 |

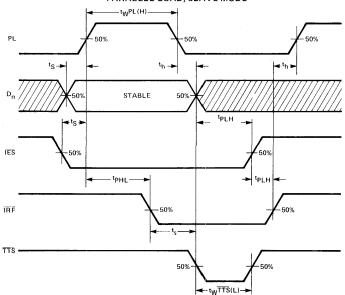

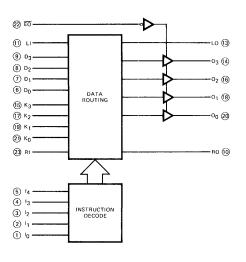

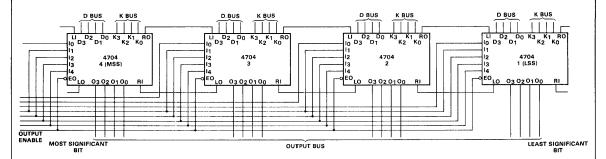

| 4704       | Data Path Switch                                | 4-40 |

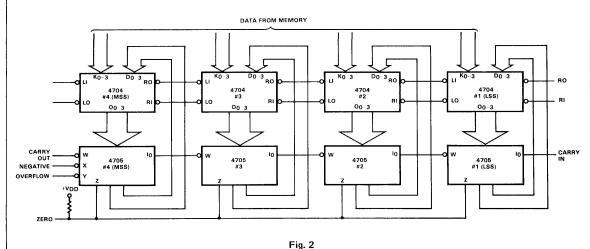

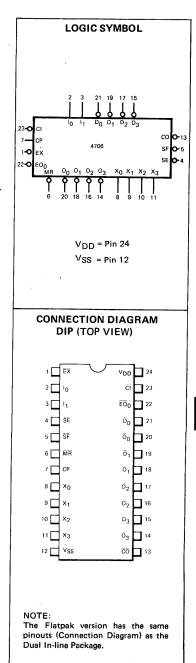

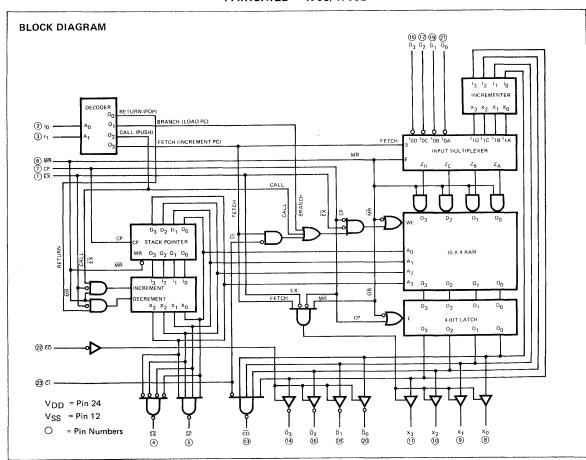

| 4705       | Arithmetic Logic Register Stack                 | 4-45 |

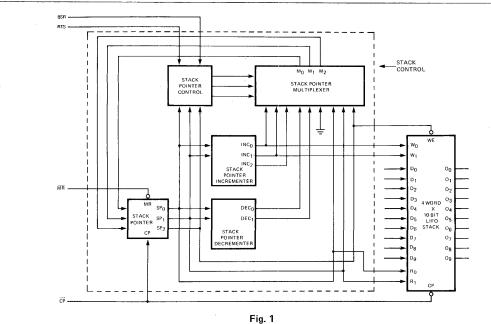

| 4706       | Program Stack                                   | 4-53 |

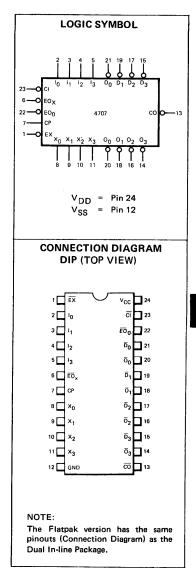

| 4707       | Data Access Register                            | 4-65 |

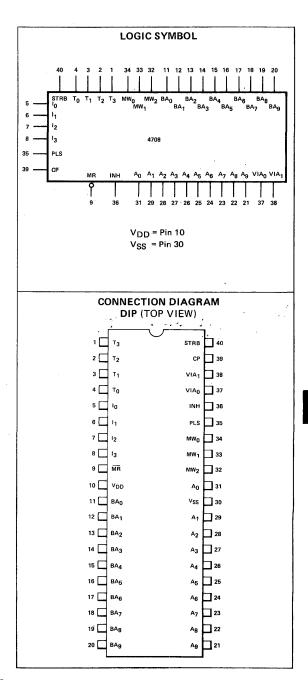

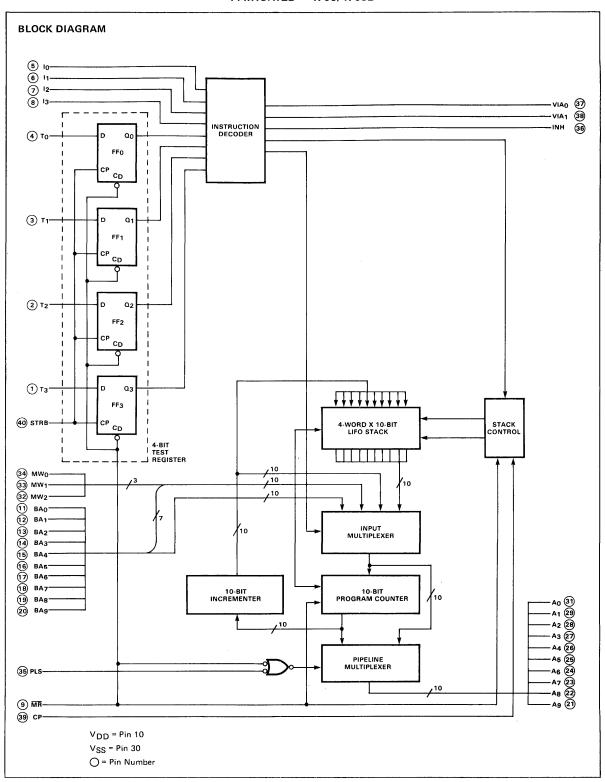

| 4708       | Microprogram Sequencer                          | 4-73 |

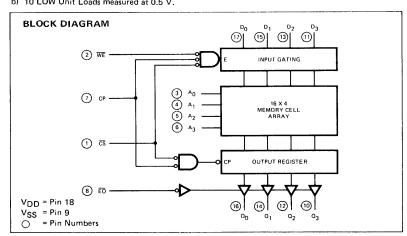

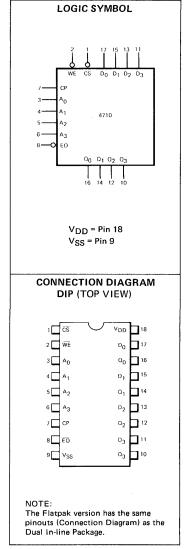

| 4710       | 16 x 4 Clocked RAM with 3-State Output Register | 4-80 |

| 9401       | CRC Generator Checker                           |      |

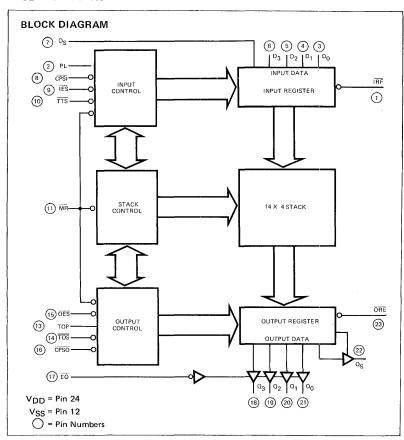

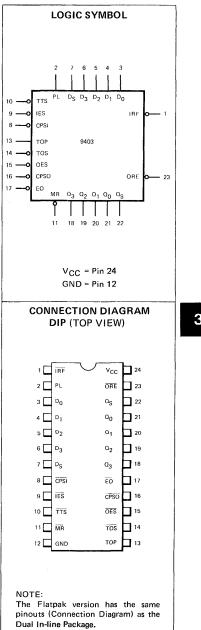

| 9403       | FIFO Buffer Memory                              | 3-15 |

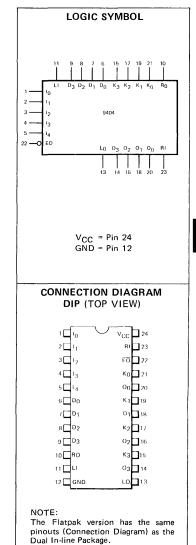

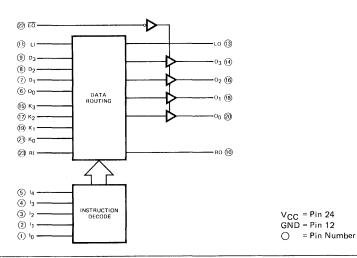

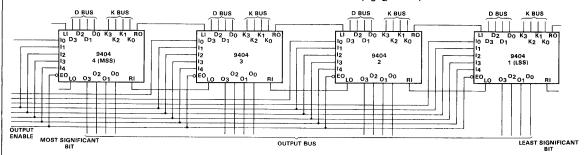

| 9404       | Data Path Switch                                | 3-29 |

| 9405       | Arithmetic Logic Register Stack                 | 3-33 |

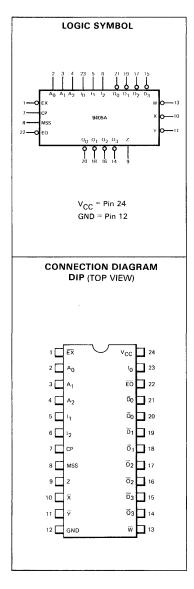

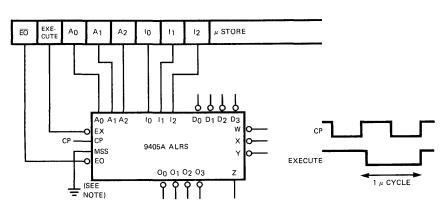

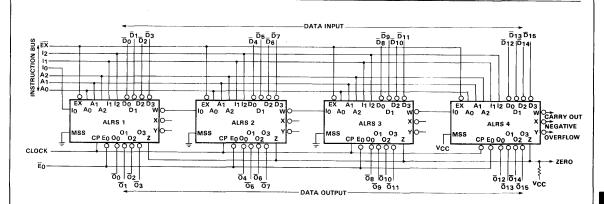

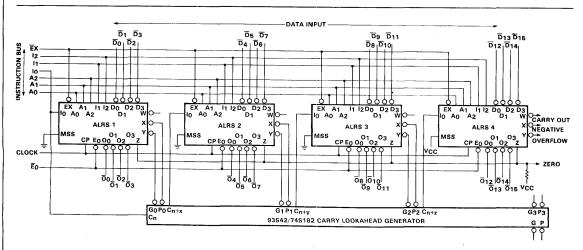

| 9405A      | 9405 with Register-to-Register Transfer         | 3-40 |

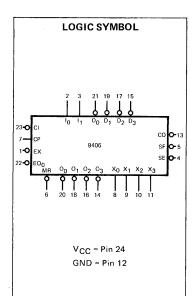

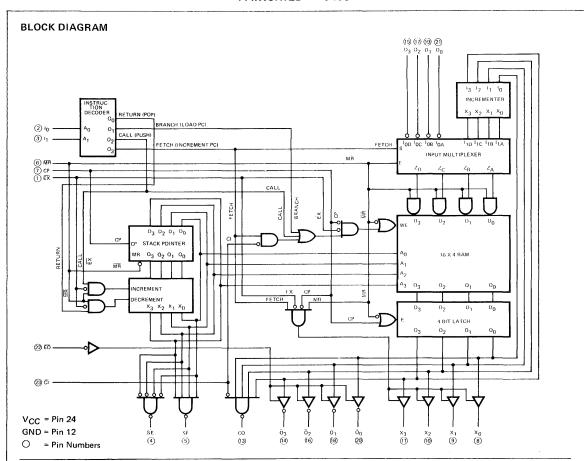

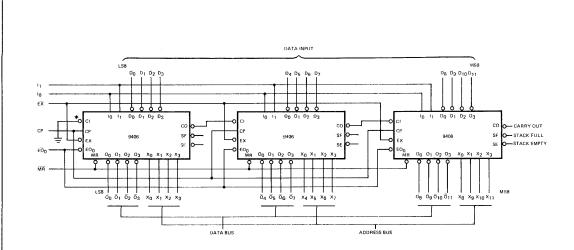

| 9406       | Program Stack                                   | 3-53 |

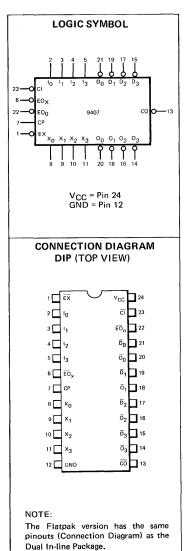

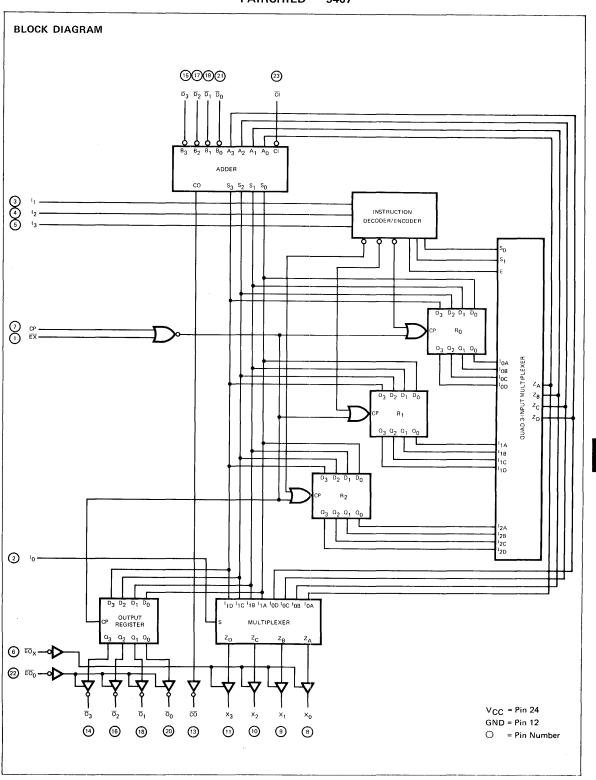

| 9407       | Data Access Register                            | 3-64 |

| 9408       | Microprogram Sequencer                          | 3-71 |

| 9410       | 16 x 4 Clocked RAM with 3-State Output Register | 3-78 |

# **DEVICE SELECTOR GUIDE BY FUNCTION**

| FUNCTION                        | DEVICE NO.          | TECHNOLOGY                     |

|---------------------------------|---------------------|--------------------------------|

| Address Arithmetic              | . 4707, 9407        | CMOS, LS                       |

| Arithmetic Logic Unit (ALU)     | . 4705, 9405, 9405A | CMOS, LS                       |

| Bit-Rate Generator              | . 4702              | CMOS                           |

| Byte Masking                    | . 4704, 9404        | CMOS, LS                       |

| Cyclic Redundancy Checks        |                     |                                |

| FIFO, 16 x 4 Expandable         | . 4703, 9403        | CMOS, LS                       |

| FIFO, 64 x 4 Expandable         | . 9423*             | I <sup>3</sup> L <sup>TM</sup> |

| LIFO Stack                      | . 4706, 9406        | CMOS, LS                       |

| Microprogram Sequencer          | . 4708, 9408        | CMOS, I³L™                     |

| Multiplexing                    | . 4704, 9404        | CMOS, LS                       |

| Program Counter                 |                     |                                |

| Registers, Intelligent          | . 4705, 9405, 9405A | CMOS, LS                       |

| Registers, Not Intelligent      | 4710, 9410          | CMOS, LS                       |

| Sign Extension                  | . 4704, 9404        | CMOS, LS                       |

| Stack Pointer* *To be announced |                     |                                |

# FUNCTIONAL BUILDING BLOCKS BY TECHNOLOGY

|                            |                                     | <b>Jack</b>                      | CMOS                                   |

|----------------------------|-------------------------------------|----------------------------------|----------------------------------------|

| MICROPROCESSOR<br>ELEMENTS | ALU/Register Unit<br>(9404, 9405)   | Microprogram<br>Sequencer (9408) | ALU/Register Unit<br>(4704, 4705)      |

|                            | LIFO Stack (9406)                   |                                  | LIFO Stack (4706)                      |

|                            | Address Arithmetic<br>Unit (9407)   |                                  | Address Arithmetic<br>Unit (4707)      |

|                            | Compatible Scratchpad Memory (9410) |                                  | Compatible Scratchpad<br>Memory (4710) |

|                            |                                     |                                  | Microprogram<br>Sequencer (4708)       |

| PERIPHERAL                 | 16 x 4 FIFO (9403)                  | 64 x 4 FIFO*                     | Bit-Rate Generator (4702)              |

| ELEMENTS                   | CRC Generator/<br>Checker (9401)    | CRT Controller*                  | 16 x 4 FIFO (4703)                     |

| *To be announced           |                                     |                                  | · · · · · · · · · · · · · · · · · · ·  |

# **MEMORY PRODUCTS SELECTOR GUIDE**

The following selector guide lists Fairchild memory products which will be useful when designing with Fairchild Macrologic. Device specifications for Fairchild memory products are available either as separate data sheets or within their respective technology data books — Bipolar Memory Data Book and MOS/CCD Data Book.

# **STATIC RAMS**

| TECHNOLOGY | DEVICE NO. | ORGANIZATION | ACCESS<br>TIME<br>tAA<br>MAX (TYP)<br>ns | POWER DISSIPATION PD MAX (TYP) mW | NO.<br>OF<br>PINS |  |

|------------|------------|--------------|------------------------------------------|-----------------------------------|-------------------|--|

| CMOS       | 4720       | 256 x 1      | 100                                      |                                   | 16                |  |

| CMOS       | 4721* **   | 256 x 4      | (450)                                    |                                   | 22                |  |

| CMOS       | 4736* **   | 1024 x 1     | (500)                                    |                                   | 16                |  |

| ECL        | 10145A     | 16 x 4       | 9.0                                      | (500)                             | 16                |  |

| ECL        | 10405      | 128 x 1      | 15                                       | (470)                             | 16                |  |

| ECL        | 10410      | 256 x 1      | 30                                       | (475)                             | 16                |  |

| ECL        | 10411      | 256 x 1      | 35                                       | (360)                             | 16                |  |

| ECL        | 10415      | 1024 x 1     | 60                                       | (475)                             | 16                |  |

| ECL        | 10415A     | 1024 x 1     | 35                                       | (475)                             | 16                |  |

| ECL        | 100415     | 1024 x 1     | (20)                                     | (500)                             | 24                |  |

| MOS        | 2102       | 1024 x 1     | 1000                                     | 160                               | 16                |  |

| MOS        | 2102-1     | 1024 x 1     | 450                                      | 160                               | 16                |  |

| MOS        | 2102-2     | 1024 x 1     | 650                                      | 160                               | 16                |  |

| MOS        | 2102F      | 1024 x 1     | 350                                      | 160                               | 16                |  |

| MOS        | 2102F2.    | 1024 x 1     | 250                                      | 110                               | 16                |  |

| MOS        | 2102LF     | 1024 x 1     | 350                                      | 110                               | 16                |  |

| MOS        | 2102LF2    | 1024 x 1     | 250                                      | 110                               | 16                |  |

| MOS        | 2102L1     | 1024 x 1     | 450                                      | 110                               | 16                |  |

| MOS        | 2102L2     | 1024 x 1     | 650                                      | 110                               | 16                |  |

| MOS        | 3539       | 256 x 8      | 650                                      | 275                               | 22                |  |

| MOS        | 3539-1     | 256 x 8      | 400                                      | 275                               | 22                |  |

| MOS        | 3539-2     | 256 x 8      | 500                                      | 275                               | 22                |  |

| MOS        | 3542       | 1024 x 1     | 150                                      | 200                               | 16                |  |

| MOS        | 3542-2     | 1024 x 1     | 120                                      | 200                               | 16                |  |

| MOS        | 3544**     | 1024 x 4     | 250                                      | 450                               | 18                |  |

| TTL        | 93419      | 64 x 9       | 40                                       | (725)                             | 28                |  |

| TTL        | 93410      | 256 x 1      | 60                                       | (450)                             | 16                |  |

| TTL        | 93410A     | 256 x 1      | 45                                       | (450)                             | 16                |  |

| TTL        | 93411      | 256 x 1      | 55                                       | (475)                             | 16                |  |

| TTL        | 93411A     | 256 x 1      | 45                                       | (475)                             | 16                |  |

| TTL        | 93L420     | 256 x 1      | 45                                       | (275)                             | 16                |  |

| TTL        | 93421      | 256 x 1      | 50                                       | (475)                             | 16                |  |

| TTL        | 93421A     | 256 x 1      | 40                                       | (475)                             | 16                |  |

| TTL        | 93L421     | 256 x 1      | 90                                       | (275)                             | 16                |  |

| TTL        | 93L412     | 256 x 4      | 70                                       | (250)                             | 22,24             |  |

| TTL        | 93L422     | 256 x 4      | 70                                       | (250)                             | 22,24             |  |

| TTL        | 93415      | 1024 x 1     | 70                                       | (475)                             | 16                |  |

| TTL        | 93415A     | 1024 x 1     | 45                                       | (475)                             | 16                |  |

| TTL        | 93L415     | 1024 x 1     | 95                                       | (200)                             | 16                |  |

| TTL        | 93425      | 1024 x 1     | 70                                       | (475)                             | 16                |  |

| TTL        | 93425A     | 1024 x 1     | 45                                       | (475)                             | 16                |  |

| TTL        | 93L425     | 1024 x 1     | 95                                       | (200)                             | 16                |  |

| TTL        | 93470**    | 4096 x 1     |                                          | (950)                             | 18                |  |

| TTL        | 93471**    | 4096 x 1     |                                          | (950)                             | 18                |  |

<sup>\*5.0</sup> V V<sub>DD</sub> \*\*Available 4th quarter 1976

# MEMORY PRODUCTS SELECTOR GUIDE (Cont'd)

# **DYNAMIC RAMS**

| TECHNOLOGY       | DEVICE NO. | ORGANIZATION | ACCESS<br>TIME<br>tAA<br>MAX (TYP)<br>ns | POWER DISSIPATION PD MAX (TYP) mW | NO.<br>OF<br>PINS |

|------------------|------------|--------------|------------------------------------------|-----------------------------------|-------------------|

| J <sub>3</sub> L | 93481      | 4096 x 1     | (90)                                     | (400)                             | 16                |

| MOS              | 4096-2     | 4096 x 1     | 200                                      | 350                               | 16                |

| MOS              | 4096-3     | 4096 x 1     | 250                                      | 300                               | 16                |

| MOS              | 4096-4     | 4096 x 1     | 300                                      | 250                               | 16                |

| MOS              | 4096-5     | 4096 x 1     | 350                                      | 250                               | 16                |

| MOS              | 4027-3**   | 4096 x 1     | 200                                      | 450                               | 16                |

| MOS              | 4027-4**   | 4096 x 1     | 250                                      | 450                               | 16                |

| MOS              | F16K**     | 16,384 x 1   | 200                                      | 600                               | 16                |

# ROMS

| TECHNOLOGY | DEVICE NO. | ORGANIZATION | ACCESS<br>TIME<br>tAA<br>MAX (TYP)<br>ns | POWER DISSIPATION PD MAX (TYP) mW | NO.<br>OF<br>PINS |

|------------|------------|--------------|------------------------------------------|-----------------------------------|-------------------|

| CMOS       | 4735* **   | 256 x 8      | (250)                                    |                                   | 24                |

| MOS        | 3515       | 512 x 8      | 600                                      |                                   | 24                |

| TTL        | 93457      | 256 x 4      | 45                                       | (425)                             | 16                |

| TTL        | 93467      | 256 x 4      | 45                                       | (425)                             | 16                |

| TTL        | 93431      | 512 x 4      | 50                                       | (475)                             | 16                |

| TTL        | 93441      | 512 x 4      | 50                                       | (475)                             | 16                |

| TTL        | 93432      | 512 x 8      | 55                                       | (650)                             | 24                |

| TTL        | 93442      | 512 x 8      | 55                                       | (650)                             | 24                |

| TTL        | 93454      | 1024 x 8     | 45                                       | (550)                             | 24                |

| TTL        | 93464      | 1024 x 8     | 45                                       | (550)                             | 24                |

# **PROMS**

| TECHNOLOGY | DEVICE NO. | ORGANIZATION | ACCESS<br>TIME<br><sup>†</sup> AA<br>MAX (TYP)<br>ns | POWER DISSIPATION PD MAX (TYP) mW | NO.<br>OF<br>PINS |

|------------|------------|--------------|------------------------------------------------------|-----------------------------------|-------------------|

| ECL        | 10416**    | 256 x 4      | (15)                                                 | (500)                             | 16                |

| TTL        | 93417      | 256 x 4      | 45                                                   | (425)                             | 16                |

| TTL        | 93427      | 256 x 4      | 45                                                   | (425)                             | 16                |

| TTL        | 93436      | 512 x 4      | 50                                                   | (475)                             | 16                |

| TTL        | 93446      | 512 x 4      | 50                                                   | (475)                             | 16                |

| TTL        | 93438      | 512 x 8      | 55                                                   | (650)                             | 24                |

| TTL        | 93448      | 512 x 8      | 55                                                   | (650)                             | 24                |

| TTL        | 93452**    | 1024 x 4     | (35)                                                 | (650)                             | 18                |

| TTL        | 93453**    | 1024 x 4     | (35)                                                 | (650)                             | 18                |

<sup>\*5.0</sup> V V<sub>DD</sub> \*\*Available 4th quarter 1976

| INTRODUCTION                                                       | 1 |

|--------------------------------------------------------------------|---|

| DEVICE INDEX AND<br>SELECTOR INFORMATION                           | 2 |

| BIPOLAR MACROLOGIC                                                 | 3 |

| CMOS MACROLOGIC                                                    | 4 |

| APPLICATIONS                                                       | 5 |

| ORDER AND PACKAGE INFORMATION                                      | 6 |

| FAIRCHILD FIELD SALES OFFICES,<br>REPRESENTATIVES AND DISTRIBUTORS | 7 |

# 9400 BIPOLAR MACROLOGIC SERIES

## **GENERAL DESCRIPTION**

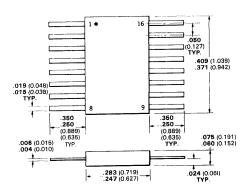

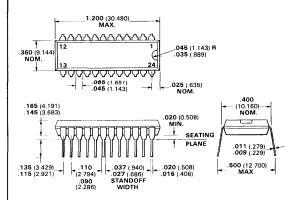

Fairchild 9400 Macrologic Series utilizes advanced Schottky and I³L™ technology to provide high performance peripheral and processor oriented LSI. The design of 9400 ensures maximum design flexibility with no performance loss. The Bipolar Macrologic elements may be used with any bit length, instruction set or organization. Devices may be expanded with little or no extra components. Where applicable, bus oriented, 3-state outputs are provided. A new, slim 24-pin package reduces PC board real estate by a third.

- 150-180 GATE COMPLEXITY

- COMPATIBLE WITH ALL TTL FAMILIES

- PERFORMANCE EQUIVALENT TO SCHOTTKY IMPLEMENTATION

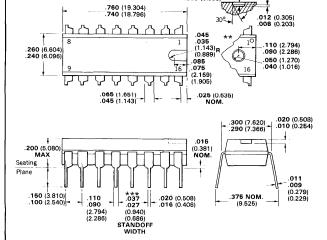

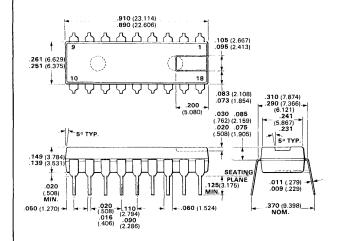

- 14, 18, SLIM 24 AND 40-PIN PACKAGES

- INPUTS ABOUT 1/4 NORMAL TTL LOAD, i.e.,  $360-400~\mu A$

- OUTPUTS DRIVE 16 mA (10 U.L.) OR 8 mA (5 U.L.)

DEPENDING ON APPLICATION

- DESIGNED FOR MAXIMUM FLEXIBILITY

- OPERATES OVER COMMERCIAL OR MILITARY TEMPERATURE RANGE

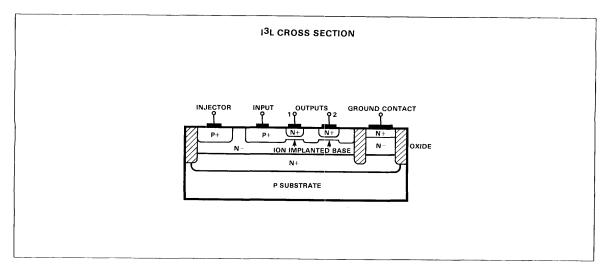

## **I3L TECHNOLOGY**

I³L™ (Isoplanar Integrated Injection Logic) combines the low power and high packing density advantages of I²L (Integrated Injection Logic) with the high speed and high packing density advantages of Fairchild's Isoplanar technology. The result is a process which offers low power (160 µW per gate), high speed (4 ns per gate) and extremely high packing density. I³L is used whenever high speed is required, but high complexity makes low power Schottky processing undesirable from a cost standpoint.

When designing with I³L Macrologic devices, TTL interface is not a problem as I³L Macrologic has standard on-chip TTL inputs and outputs. An I³L current source also is contained on-chip, therefore only a single 5 V power supply is required and the chip appears to be TTL to the user. However, because internal logic is implemented with I³L, the chip is smaller, uses less power and is less expensive than a TTL equivalent.

## **DESIGN CONSIDERATIONS**

TTL Macrologic has been designed so that its input and output levels and thresholds are equivalent to standard TTL when fan-out is no greater than 10. Therefore, the design considerations delineated on the following pages apply to Macrologic as well as any other TTL.

## Supply Voltage and Temperature Range

The nominal supply voltage (VCC) for all TTL, including 9400 Macrologic, is +5.0 V. Commercial grade parts

are guaranteed to perform with a  $\pm 5\%$  supply tolerance ( $\pm 250$  mV) over an ambient temperature range of 0°C to +75°C. MIL-grade parts are guaranteed to perform with a  $\pm 10\%$  supply tolerance ( $\pm 500$  mV) over an ambient temperature range of -55°C to +125°C.

TTL families may be mixed for optimum system design. The following tables specify the worst case noise immunity in mixed systems.

# Worst Case TTL DC Noise Immunity / Noise Margins

#### **Electrical Characteristics**

|        |                                        | Military (-55 to +125°C) Commercial (0 to 75°C) |     |     |     |     |     |     |     |       |

|--------|----------------------------------------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-------|

| Symbol | Fairchild TTL Families                 | VIL                                             | VIH | VOL | Vон | VIL | VIH | VOL | VOH | Units |

| TTL    | Standard TTL 9000, 9N (54/74)          | 0.8                                             | 2.0 | 0.4 | 2.4 | 0.8 | 2.0 | 0.4 | 2.4 | V     |

| HTTL   | High Speed TTL 9H (54H/74H)            | 0.8                                             | 2.0 | 0.4 | 2.4 | 0.8 | 2.0 | 0.4 | 2.4 | V     |

| LPTTL  | Low Power TTL, 93L00 (MSI)             | 0.7                                             | 2.0 | 0.3 | 2.4 | 0.8 | 2.0 | 0.3 | 2.4 | V     |

| STTL   | Schottky TTL 9S (54S/74S), 93S00       | 0.8                                             | 2.0 | 0.5 | 2.5 | 0.8 | 2.0 | 0.5 | 2.7 | V     |

| LSTTL  | Low Power Schottky TTL 9LS (54LS/74LS) | 0.7                                             | 2.0 | 0.4 | 2.5 | 0.8 | 2.0 | 0.5 | 2.7 | V     |

$V_{OL}$  and  $V_{OH}$  are the voltages generated at the output.  $V_{IL}$  and  $V_{IH}$  are the voltage required at the input to generate the appropriate output levels. The numbers given above are guaranteed worst-case values.

# LOW Level Noise Margins (Military)

#### TTL HTTL LPTTL STTL LSTTL Units From TTL 400 400 300 400 300 mV mV HTTL 400 400 300 400 300 mV LPTTL 500 400 500 400 500 mV 300 200 300 200 STTL 300 400 400 300 400 300 mV LSTTL

From "VOL" to "VIL

#### HIGH Level Noise Margins (Military)

| From To | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|---------|-----|------|-------|------|-------|-------|

| TTL     | 400 | 400  | 400   | 400  | 400   | mV    |

| HTTL    | 400 | 400  | 400   | 400  | 400   | mV    |

| LPTTL   | 400 | 400  | 400   | 400  | 400   | mV    |

| STTL    | 500 | 500  | 500   | 500  | 500   | mV    |

| LSTTL   | 500 | 500  | 500   | 500  | 500   | mV    |

From "VOH" to "VIH"

## LOW Level Noise Margins (Commercial)

| EO II EOIO. |     |      |       |      |       |       |

|-------------|-----|------|-------|------|-------|-------|

| From To     | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

| TTL         | 400 | 400  | 400   | 400  | 400   | mV    |

| HTTL        | 400 | 400  | 400   | 400  | 400   | mV    |

| LPTTL       | 500 | 500  | 500   | 500  | 500   | mV    |

| STTL        | 300 | 300  | 300   | 300  | 300   | mV    |

| LSTTL       | 300 | 300  | 300   | 300  | 300   | mV    |

From "VOL" to "VIL"

# HIGH Level Noise Margins (Commercial)

| From To | TTL | HTTL | LPTTL | STTL | LSTTL | Units |

|---------|-----|------|-------|------|-------|-------|

| TTL     | 400 | 400  | 400   | 400  | 400   | mV    |

| HTTL    | 400 | 400  | 400   | 400  | 400   | mV    |

| LPTTL   | 400 | 400  | 400   | 400  | 400   | mV    |

| STTL    | 700 | 700  | 700   | 700  | 700   | mV    |

| LSTTL   | 700 | 700  | 700   | 700  | 700   | mV    |

From "VOH" to "VIH"

# Fan-in and Fan-out

In order to simplify designing with Fairchild TTL devices, the input and output loading parameters of all families are normalized to the values shown at the right.

Input loading and output drive factors of all products described in this handbook are related to these definitions

- 1 TTL Unit Load (U.L.) = 40  $\mu$ A in the HIGH state (logic "1")

- 1 TTL Unit Load (U.L.) = 1.6 mA in the LOW state (logic "0")

- 1. A 9N00/7400 gate, which has a maximum I $_{\rm IL}$  of 1.6 mA and I $_{\rm IH}$  of 40  $\mu$ A is specified as having an input load factor of 1 U.L. (Also called a fan-in of 1 load.)

- 2. The 9LS95 which has a value of  $I_{IL}$  = 0.8 mA and  $I_{IH}$  of 40  $\mu$ A on the CP terminal, is specified as having an input LOW load factor of

$$\frac{0.8 \text{ mA}}{1.6 \text{ mA}}$$

or 0.5 U.L.

and an input HIGH load factor of

$$\frac{40 \mu A}{40 \mu A}$$

or 1 U.L.

3. The 9LS00 gate which has an I<sub>IL</sub> of 0.36 mA and an I<sub>IH</sub> of 20  $\mu$ A, has an input LOW load factor of

$$\frac{0.36 \text{ mA}}{1.6 \text{ mA}}$$

or 0.225 U.L.

(normally rounded to 0.25 U.L.) and an input HIGH load factor of

$$\frac{20 \ \mu A}{40 \ \mu A}$$

or 0.5 U.L.

Examples - Output Drive

1. The output of the 9N00/7400 will sink 16 mA in the LOW (logic "0") state and source 800  $\mu$ A in the HIGH (logic "1") state. The normalized output LOW drive factor is therefore

$$\frac{16 \text{ mA}}{1.6 \text{ mA}} = 10 \text{ U.L.}$$

and the output HIGH drive factor is

$$\frac{800 \ \mu A}{40 \ \mu A}$$

or 20 U.L.

2. The output of the 9LS00XC (Commercial Grade) will sink 8.0 mA in the LOW state and source 400  $\mu$ A in the HIGH state. The normalized output LOW drive factor is

$$\frac{8.0 \text{ mA}}{1.6 \text{ mA}}$$

or 5 U.L.

and the output HIGH drive factor is

$$\frac{400 \,\mu\text{A}}{40 \,\mu\text{A}}$$

or 10 U.L.

Relative load and drive factors for the basic TTL families are given in *Table I*.

TABLE I

| FAMILY     | INPUT     | LOAD      | OUTPUT DRIVE |           |  |

|------------|-----------|-----------|--------------|-----------|--|

| - AWIL     | HIGH      | LOW       | HIGH         | LOW       |  |

| 9LS00      | 0.5 U.L.  | 0.25 U.L. | 10 U.L.      | 5 U.L.    |  |

| 9N00/7400  | 1 U.L.    | 1 U.L.    | 20 U.L.      | 10 U.L.   |  |

| 9000       | 1 U.L.    | 1 U.L.    | 20 U.L.      | 10 U.L.   |  |

| 9H00/74H00 | 1.25 U.L. | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |  |

| 9S00/74S00 | 1.25 U.L. | 1.25 U.L. | 25 U.L.      | 12.5 U.L. |  |

Values for MSI devices vary significantly from one element to another. Consult the appropriate data sheet for actual characteristics.

#### Wired-OR Applications

Certain TTL devices are provided with an "open" collector output to permit the Wired-OR (actually Wired-AND) function. This is achieved by connecting open collector outputs together and adding an external pull-up resistor.

The value of the pull-up resistor is determined by considering the fan-out of the OR tie and the number of devices in the OR tie. The pull-up resistor value is chosen from a range between a maximum value (established to maintain the required  $V_{OH}$  with all the OR tied outputs HIGH) and a minimum value (established so that the OR tie fan-out is not exceeded when only one output is LOW).

Minimum and Maximum Pull-Up Resistor Values

$$R_{X(MIN)} = \frac{V_{CC(MAX)} - V_{OL}}{I_{OL} - N_2(LOW) \cdot 1.6 \text{ mA}}$$

$$R_{X(MAX)} = \frac{V_{CC(MIN)} - V_{OH}}{N_1 \bullet I_{OH} + N_2(HIGH) \bullet 40 \mu A}$$

where:

R<sub>X</sub> = External Pull-up Resistor N<sub>1</sub> = Number of Wired-OR Outputs

N<sub>2</sub> = Number of Input Unit Loads being Driven

I<sub>OH</sub> = I<sub>CEX</sub> = Output HIGH Leakage Current

IOL = LOW Level Fan-out Current of Driving Element

V<sub>OL</sub> = Output LOW Voltage Level (0.5 V) V<sub>OH</sub> = Output HIGH Voltage Level (2.4 V)

V<sub>CC</sub> = Power Supply Voltage

Example: Four 9LS03 gate outputs driving four other 9LS gates or MSI inputs.

$$R_{X(MIN)} = \; \frac{5.25 \; V - 0.5 \; V}{8 \; mA - 1.6 \; mA} \; = \frac{4.75 \; V}{6.4 \; mA} \; = 742 \; \Omega$$

$$R_{X(MAX)} = \frac{4.75 \text{ V} - 2.4 \text{ V}}{4 \cdot 100 \,\mu\text{A} + 2 \cdot 40 \,\mu\text{A}} = \frac{2.35 \text{ V}}{0.48 \text{ mA}} = 4.9 \text{ k}\Omega$$

where:

$N_1 = 4$

$N_2(HIGH) = 4 \cdot 0.5 \text{ U.L.} = 2 \text{ U.L.}$  $N_2(LOW) = 4 \cdot 0.25 \text{ U.L.} = 1 \text{ U.L.}$

$I_{OH}$  = 100  $\mu$ A  $I_{OL}$  = 8 mA  $V_{OL}$  = 0.5 V  $V_{OH}$  = 2.4 V

Any value of pull-up resistor between 742  $\Omega$  and 4.9 k $\Omega$  can be used. The lower values yield the fastest speeds; the higher values yield the lowest power dissipation.

#### **Unused Inputs**

For best noise immunity and switching speed, unused TTL inputs should not be left floating. These inputs should be held between 2.4 V and the absolute maximum input voltage.

Two possible ways of handling unused inputs are:

- 1. Connect unused input to  $V_{CC}$ . Most 9LS inputs have a breakdown voltage > 15 V and require, therefore, no series resistor. For all multi-emitter conventional TTL inputs, a 1 to 10 k $\Omega$  current limiting series resistor is recommended, to protect against  $V_{CC}$  transients that exceed 5.5 V.

- 2. Connect the unused input to the output of un unused gate that is forced HIGH.

CAUTION: Do not connect an unused LSTTL input to another input of the same NAND or AND function. This method, recommended for normal TTL, increases the input coupling capacitance and thus reduces the ac noise immunity.

#### Interconnection Delays

For those parts of a system in which timing is critical, designers should take into account the finite delay along the interconnections. This delay ranges from about 0.12 to 0.15 ns/inch for the type of interconnections normally used in TTL systems. Exceptions occur in systems using ground planes with STTL to reduce ground noise during a logic transition; ground planes give higher distributed capacitance and delays of about 0.15 to 0.22 ns/inch.

Most interconnections on a logic board are short enough that the wiring and load capacitance can be treated as a lumped capacitance for purposes of estimating their effect on the propagation delay of the driving circuit. When an interconnection is long enough that its delay is one-fourth to one-half of the signal transition time, the driver output waveform exhibits noticeable slope changes during a transition. This is evidence that during the initial portion of the output voltage transition the driver sees the characteristic impedance of the interconnection (normally  $150 \Omega$  to  $200 \Omega$ ), which for transient conditions appears as a resistor returned to the quiescent voltage existing just before the beginning of the transition. This characteristic impedance forms a voltage divider with the driver output impedance, tending to produce a signal transition having the same rise or fall time as in the no-load condition but with a reduced amplitude. This attenuated signal travels to the far end of the interconnection, which is essentially an unterminated transmission line, whereupon the signal starts doubling. Simultaneously, a reflection voltage is generated which has the same amplitude and polarity as the original signal, e.g., if the driver output signal is positive-going the reflection will be positive-going, and as it travels back toward the driver it adds to the line voltage. At the instant the reflection arrives at the driver it adds algebraically to the still-rising driver output, accelerating the transition rate and producing the noticeable change in slope.

If an interconnection is of such length that its delay is longer than half the signal transition time, the attenuated output of the driver has time to reach substantial completion before the reflection arrives. In the limit, the waveform observed at the driver output is a 2-step signal with a pedestal. In this circumstance the first load circuit to receive a full signal is the one at the far end, because of the doubling effect, while the last one to receive a full signal is the one nearest the driver since it must wait for the reflection to complete the transition. Thus, in a worst-cast situation, the net contribution to the overall delay is twice the delay of the interconnection because the initial part of the signal must travel to the far end of the line and the reflection must return.

When load circuits are distributed along an interconnection, the input capacitance of each will cause a small reflection having a polarity opposite that of the signal transition, and each capacitance also slows the transition rate of the signal as it passes by. The series of small reflections, arriving back at the driver, is subtractive and has the effect of reducing the apparent amplitude of the signal. The successive slowing of the transition rate of the transmitted signal means that it takes longer for the signal to rise or fall to the threshold level of any particular load circuit. A rough but workable approach is to treat the load capacitances as an increase in the intrinsic distributed capacitance of the interconnection. Increasing the distributed capacitance of a transmission line reduces its impedance and increases its delay. A good approximation for ordinary TTL interconnections is that distributed load capacitance decreases the characteristic impedance by about one-third and increases the delay by one-half.

Another advantage of LSTTL has to do with its output impedance during a positive-going transition. Whereas the low output impedance of STTL and HTTL allows

these circuits to force a larger initial swing into a low impedance interconnection, the low output impedance also has a disadvantage. It makes the reflection coefficient negative at the driven end of the interconnection, a circumstance that exists any time a transmission line is terminated by an impedance lower than its characteristic impedance. This means that when the reflection from the (essentially) open end of the interconnection arrives back at the driver it will be re-reflected with the opposite polarity. The result is a sequence of reflected signals which alternate in sign and decrease in magnitude, commonly known as ringing. The lower the driver output impedance, the greater the amplitude of the ringing and the longer it takes to damp out.

The output impedance of LSTTL, on the other hand, is closer to the characteristic impedance of the interconnections commonly used with TTL, and ringing is practically non-existent. Thus no special packaging is required. This advantage, combined with excellent speed, modest edge rates and very low transient currents, are some of the reasons that designers have found LSTTL extremely easy to work with and very cost effective.

# **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA BOOK**

**CURRENTS** — Positive current is defined as conventional current flow into a device. Negative current is defined as conventional current flow out of a device. All current limits are specified as absolute values.

|    |                      | ·                                                                                                                                                                                                                                                       |

|----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lC | CC                   | Supply current – The current flowing into the $V_{CC}$ supply terminal of a circuit with the specified input conditions and the outputs open. When not specified, input conditions are chosen to guarantee worst case operation.                        |

| Щ  | н                    | Input HIGH current — The current flowing into an input when a specified HIGH voltage is applied.                                                                                                                                                        |

| Ч  | L                    | $\label{low-current} \textbf{Input LOW current} - \textbf{The current flowing out of an input when a specified LOW voltage} \\ \textbf{is applied.}$                                                                                                    |

| Ic | DН                   | Output HIGH current — The leakage current flowing into a turned off open collector output with a specified HIGH output voltage applied. For devices with a pull-up circuit, the IOH is the current flowing out of an output which is in the HIGH state. |

| I  | DL                   | Output LOW current - The current flowing into an output which is in the LOW state.                                                                                                                                                                      |

| Ic | os                   | Output short circuit current — The current flowing out of an output which is in the HIGH state when that output is short circuited to ground (or other specified potential).                                                                            |

| I  | OZH                  | Output off HIGH current – The current flowing into a disabled 3-state output with a specified HIGH output voltage applied.                                                                                                                              |

| I  | OZL                  | Output off LOW current — The current flowing out of a disabled 3-state output with a specified LOW output voltage applied.                                                                                                                              |

|    |                      | $^-$ All voltages are referenced to ground. Negative voltage limits are specified as absolute 10 V is greater than $^-$ 1.0 V).                                                                                                                         |

| ٧  | ′cc                  | Supply voltage $-$ The range of power supply voltage over which the device is guaranteed to operate within the specified limits.                                                                                                                        |

| ٧  | CD(MAX)              | Input clamp diode voltage — The most negative voltage at an input when 18 mA is forced out of that input terminal. This parameter guarantees the integrity of the input diode which is intended to clamp negative ringing at the input terminal.        |

| ٧  | ⁄ін                  | Input HIGH voltage — The range of input voltages that represents a logic HIGH in the system.                                                                                                                                                            |

| ١  | /IH(MIN)             | <b>Minimum input HIGH voltage</b> $-$ The minimum allowed input HIGH in a logic system. This value represents the guaranteed input HIGH threshold for the device.                                                                                       |

| ١  | /IL                  | Input LOW voltage - The range of input voltages that represents a logic LOW in the system.                                                                                                                                                              |

| ١  | <sup>/</sup> IL(MAX) | <b>Maximum input LOW voltage</b> — The maximum allowed input LOW in a system. This value represents the guaranteed input LOW threshold for the device.                                                                                                  |

| ١  | OH(MIN)              | Output HIGH voltage – The minimum voltage at an output terminal for the specified output current $I_{OH}$ and at the minimum value of $V_{CC}$ .                                                                                                        |

|    |                      |                                                                                                                                                                                                                                                         |

V<sub>OL</sub>(MAX)

specified load current IOL.

Output LOW voltage - The maximum voltage at an output terminal sinking the maximum

# **DEFINITION OF SYMBOLS AND TERMS USED IN THIS DATA BOOK (Cont'd)**

- V<sub>T+</sub>

Positive-going threshold voltage The input voltage of a variable threshold device (i.e., Schmitt Trigger) that is interpreted as a V<sub>IH</sub> as the input transition rises from below V<sub>T</sub>-(MIN).

- V<sub>T</sub>-- Negative-going threshold voltage The input voltage of a variable threshold device (i.e., Schmitt Trigger) that is interpreted as a V<sub>IL</sub> as the input transition falls from above V<sub>T</sub>+(MAX).

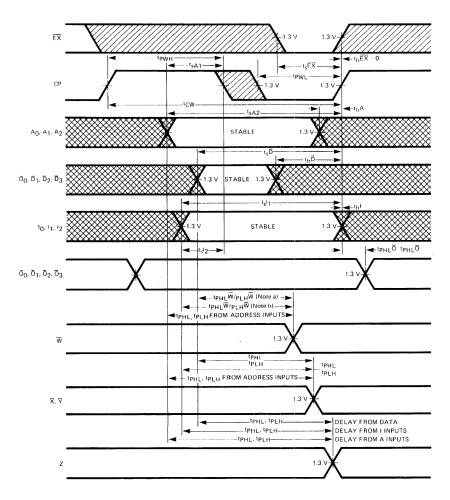

## **AC SWITCHING PARAMETERS**

- f<sub>MAX</sub>

Toggle frequency/operating frequency The maximum rate at which clock pulses may be applied to a sequential circuit. Above this frequency the device may cease to function.

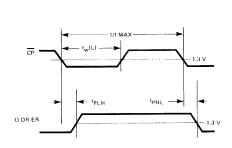

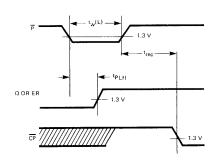

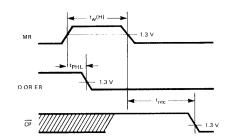

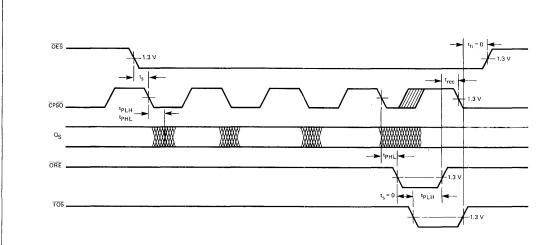

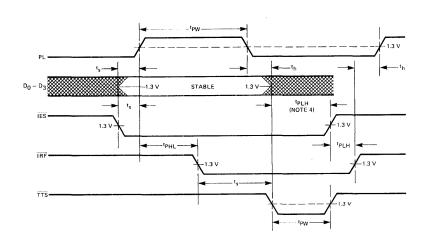

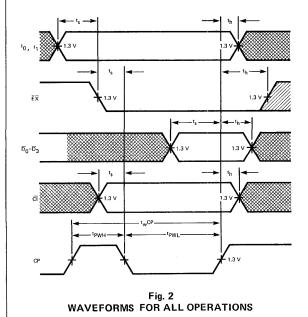

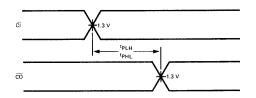

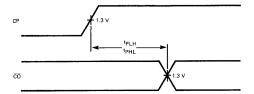

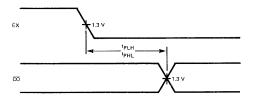

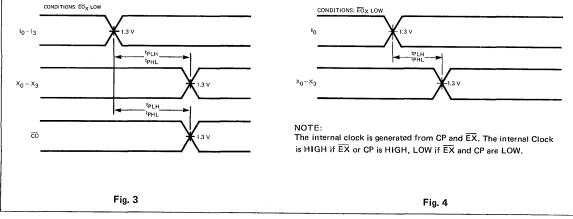

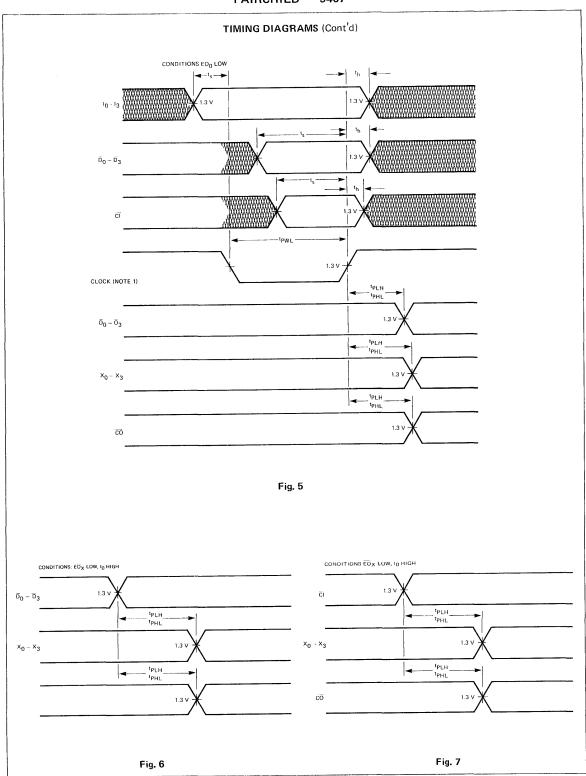

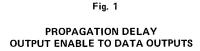

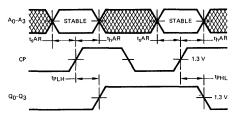

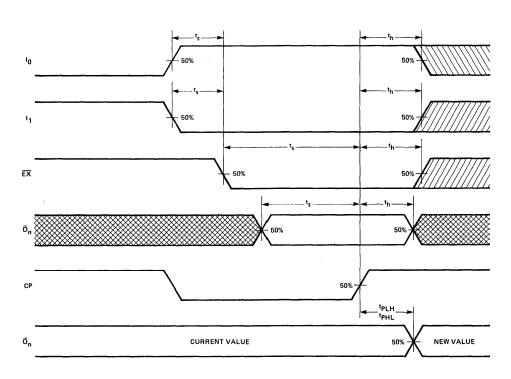

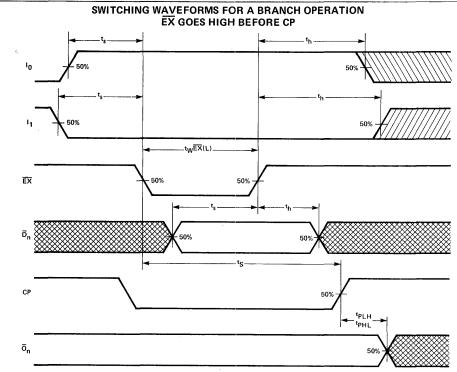

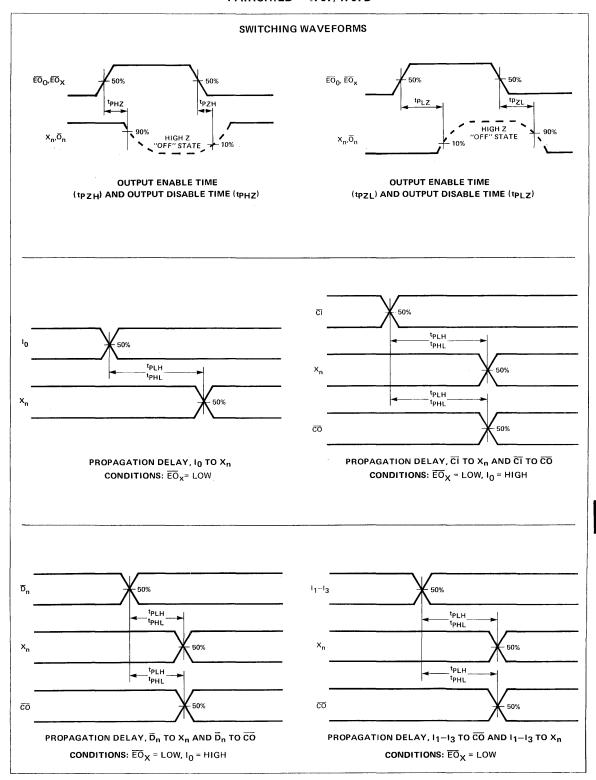

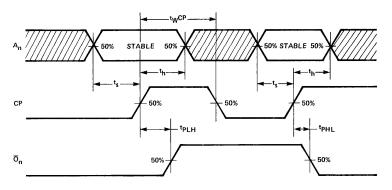

- tpLH Propagation delay time The time between the specified reference points, normally 1.3 V on the input and output voltage waveforms, with the output changing from the defined LOW level to the defined HIGH level.

- tpHL Propagation delay time The time between the specified reference points, normally 1.3 V on the input and output voltage waveforms, with the output changing from the defined HIGH level to the defined LOW level.

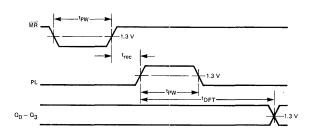

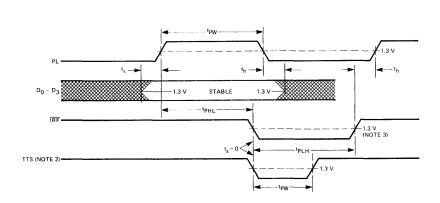

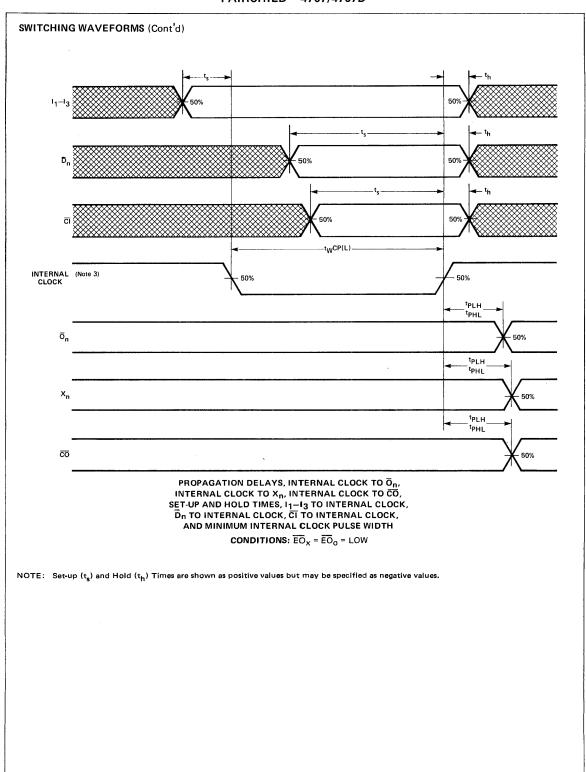

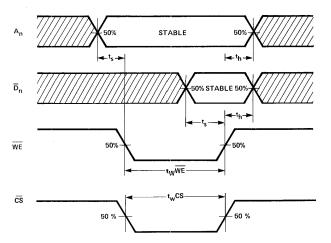

- tw Pulse width The time between 1.3 V amplitude points on the leading and trailing edges of a pulse.

- th

Hold time The interval immediately following the active transition of the timing pulse (usually the clock pulse) or following the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its continued recognition. A negative hold time indicates that the correct logic level may be released prior to the active transition of the timing pulse and still be recognized.

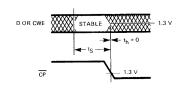

- Set-up time The interval immediately preceding the active transition of the timing pulse (usually the clock pulse) or preceding the transition of the control input to its latching level, during which interval the data to be recognized must be maintained at the input to ensure its recognition. A negative set-up time indicates that the correct logic level may be initiated sometime after the active transition of the timing pulse and still be recognized.

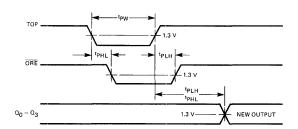

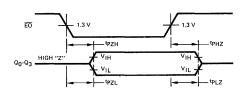

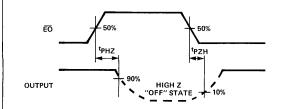

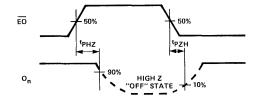

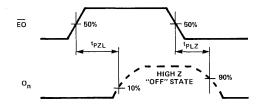

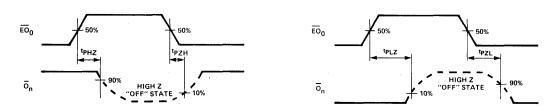

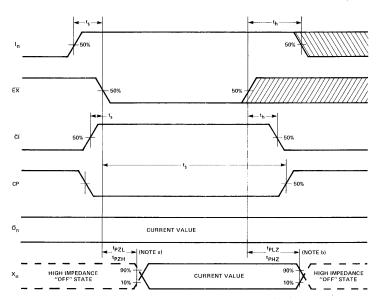

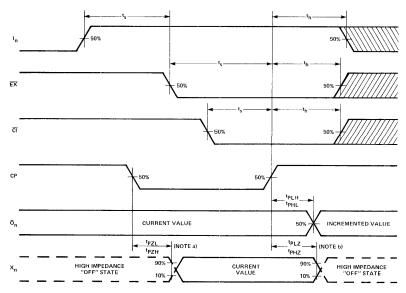

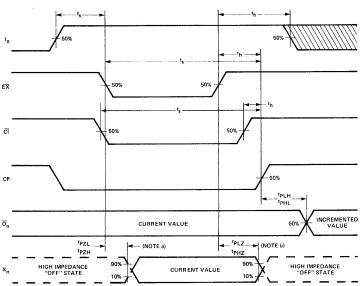

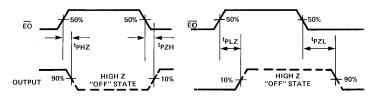

- tpHZ

Output disable time (of a 3-state output) from HIGH level The time between the 1.3 V level on the input and a voltage 0.5 V below the steady state output HIGH level with the 3-state output changing from the defined HIGH level to a high-impedance (off) state.

- tpLZ

Output disable time (of a 3-state output) from LOW level The time between the 1.3 V level on the input and a voltage 0.5 V above the steady state output LOW level with the 3-state output changing from the defined LOW level to a high-impedance (off) state.

- Output enable time (of a 3-state output) to a HIGH level The time between the 1.3 V levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a HIGH level.

- Output enable time (of a 3-state output) to a LOW level The time between the 1.3 V levels of the input and output voltage waveforms with the 3-state output changing from a high-impedance (off) state to a LOW level.

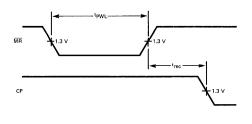

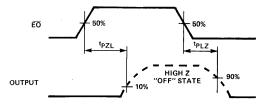

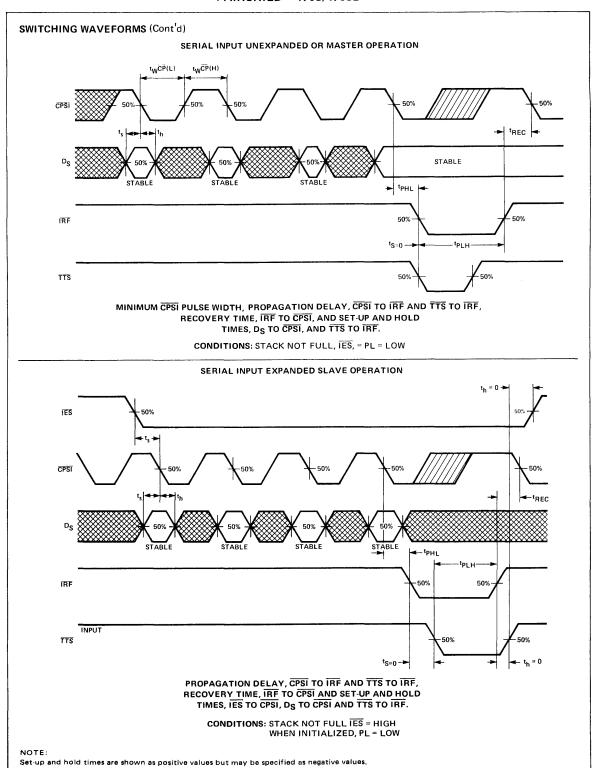

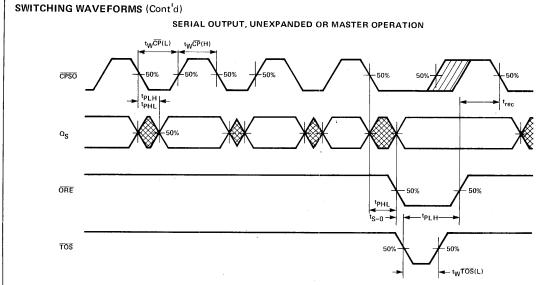

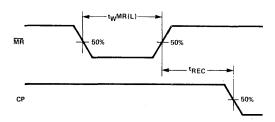

- t<sub>rec</sub>

Recovery time The time between the 1.3 V level on the trailing edge of an asynchronous input control pulse and the 1.3 V level on a synchronous input (clock) pulse such that the device will respond to the synchronous input.

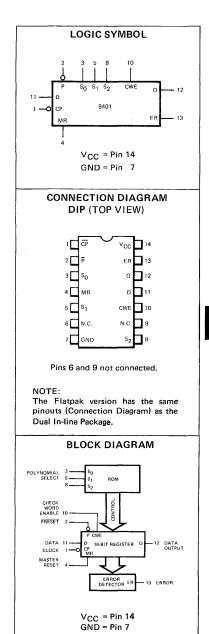

# 9401

# CRC GENERATOR/CHECKER

# FAIRCHILD TTL MACROLOGIC

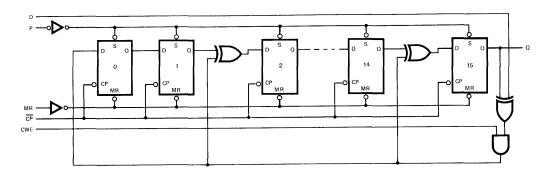

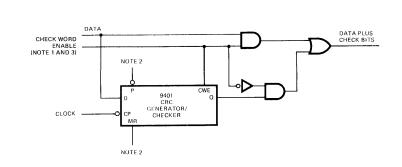

**DESCRIPTION** - The 9401 Cycle Redundancy Check (CRC) Generator/Checker provides an advanced tool for implementing the most widely used error detection scheme in serial digital data handling systems. A 3-bit control input selects one-of-eight generator polynomials. The list of polynomials includes CRC-16 and CRC-CCITT as well as their reciprocals (reverse polynomials). Automatic right justification is incorporated for polynomials of degree less than 16. Separate clear and preset inputs are provided for floppy disc and other applications. The Error output indicates whether or not a transmission error has occurred. Another control input inhibits feedback during check word transmission. The 9401 is fully compatible with all TTL families.

- GUARANTEED 10 MHz DATA RATE

- **EIGHT SELECTABLE POLYNOMIALS**

- ERROR INDICATOR

- SEPARATE PRESET AND CLEAR CONTROLS

- **AUTOMATIC RIGHT JUSTIFICATION**

- FULLY COMPATIBLE WITH ALL TTL LOGIC FAMILIES

- 14-PIN PACKAGE

- TYPICAL APPLICATIONS:

FLOPPY AND OTHER DISC STORAGE SYSTEMS **DIGITAL CASSETTE AND CARTRIDGE SYSTEMS DATA COMMUNICATION SYSTEMS**

| PIN NAMES   |                                  | LOADING  | G (Note a)             |

|-------------|----------------------------------|----------|------------------------|

|             |                                  | HIGH     | LOW                    |

| $s_0 - s_2$ | Polynomial Select Inputs         | 1.0 U.L. | 0.23 U.L.              |

| D<br>CP     | Data Input                       | 1.0 U.L. | 0.23 U.L.              |